MILŁPRFŁ55110G

APPENDIX A

A.3.6.9

A.3.6.9 Plating and coating properties.

A.3.6.9.1

A.3.6.9.1 Plating and coating thickness (when applicable). Unless otherwise specified (see A.3.1.1), the plating or

table AŁI TABLE AŁI

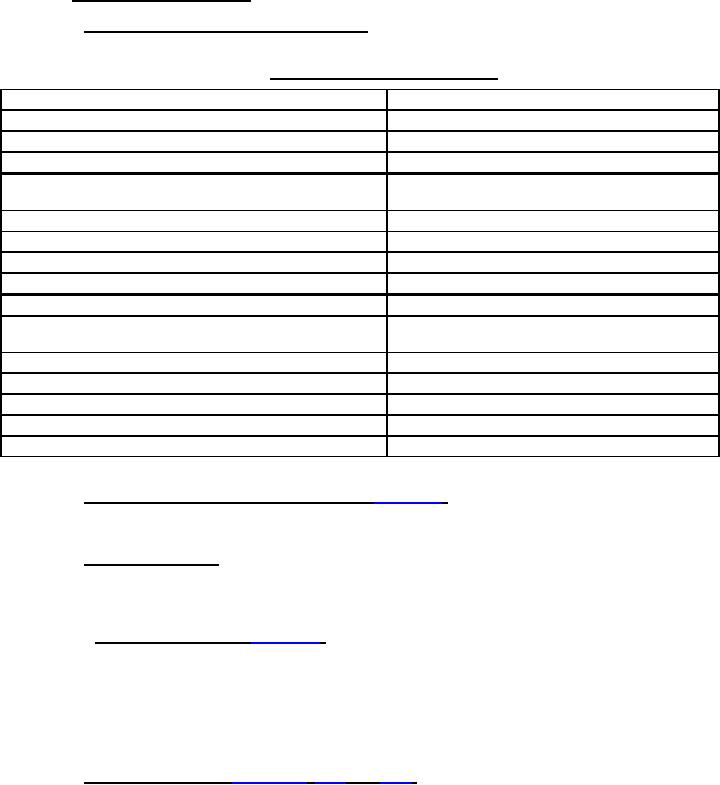

TABLE AŁI. Conductor plating and finish thickness.

Material

Thickness, in inches

Copper (in holes, blind vias, surface)

.001 (0.025 mm)

Copper (buried vias)

.0006 (0.015 mm)

Copper (low aspect ratio blind vias, blind microvias)

.00047 (0.012 mm)

Gold (for edge-board contacts and areas not to be soldered)

.00005 (0.0013 mm)

(minimum)

Gold (on areas to be soldered) (maximum)

.000018 (0.00046 mm)

Gold (on areas to be wire bonded, ultrasonic) (minimum)

.000002 (0.00005 mm)

Gold (on areas to be wire bonded, thermosonic) (minimum)

.00003 (0.0008 mm)

Immersion gold

.000002 to .000009 (0.00005 to 0.00023 mm)

Nickel (for edge-board contacts) (minimum)

.0001 (0.0025 mm)

Nickel (barrier to prevent formation of copper-tin compounds)

.0002 (0.005 mm)

(minimum)

Nickel, Electroless

.0001 to .0002 (0.0025 to 0.005 mm)

Organic Solderabilty Preservative (OSP), immersion silver

Solderable

Tin-lead, fused or solder coat

Coverage and solderable

Tin-lead, unfused

.0003 (0.008 mm)

Solder coat over base copper

Coverage and solderable

A.3.6.9.2

A.3.6.9.2 Copper plating thickness (when applicable) (see figure AŁ13). Copper plating thickness (on the surface,

in plated-through holes, buried vias, blind vias, and low aspect ratio blind vias) shall be as specified (see A.3.1.1). If

not specified on the master drawing, the copper plating shall comply with the thicknesses defined in table AŁI.

A.3.6.9.3

A.3.6.9.3 Copper plating defects. Unless otherwise specified (see A.3.1.1), a 20 percent reduction of the specified

copper plating thickness shall be acceptable if it is non-continuous (isolated; not more than 10 percent of the

composite board thickness). Any copper plating less than 80 percent of the specified thickness shall be treated as a

copper plating void.

A.3.6.9.3.1

A.3.6.9.3.1 Copper plating voids (see figure AŁ14). The copper plating in the plated holes shall not exhibit any

void in excess of the following:

a.

There shall be no more than one plating void per panel, regardless of length or size.

b.

There shall be no plating void in excess of 5 percent of the total printed wiring board thickness.

c. There shall be no plating voids evident at the interface of an internal conductive layer and plated hole wall.

A.3.6.9.4

A.3.6.9.4 Plating separations (see figures AŁ15, AŁ16, and A.7.3). Except for along the vertical edge of the

external copper foil, there shall be no separations or contamination between the hole wall conductive interfaces.

Conductive interface separations along the vertical edge of the external copper foil shall be acceptable.

16

For Parts Inquires submit RFQ to Parts Hangar, Inc.

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business