MIL-DTL-62739A(AT)

4.2.3.5.3 Clock count and latch. To determine conformance to 3.3.5.3, apply the

waveforms in figure 7 to clear and latch the real time clock count. The frequency of the signal

applied to P1-45 shall be between 50 kHz and 410 kHz. The waveforms in figure 8 shall be

applied to read the most and least significant bytes of the real time clock latch.

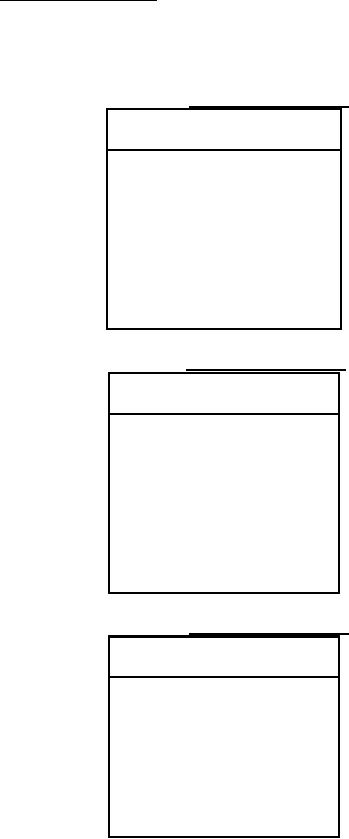

TABLE IV. Display driver outputs.

BUS 7

BUS 0

Active

(MSB)

(LSB)

output

0 0 0 0

0 0 0 1

P1-58

0 0 0 0

0 0 1 0

P1-61

0 0 0 0

0 1 0 0

P1-60

0 0 0 0

1 0 0 0

P1-64

0 0 0 1

0 0 0 0

P1-63

0 0 1 0

0 0 0 0

P1-59

0 1 0 0

0 0 0 0

P1-57

1 0 0 0

0 0 0 0

P1-62

0 0 0 0

0 0 0 0

------

TABLE V. Display driver outputs.

BUS 7

BUS 0

Active

(MSB)

(LSB)

output

0 0 0 0

0 0 0 1

P1-66

0 0 0 0

0 0 1 0

P1-69

0 0 0 0

0 1 0 0

P1-68

0 0 0 0

1 0 0 0

P1-72

0 0 0 1

0 0 0 0

P1-71

0 0 1 0

0 0 0 0

P1-67

0 1 0 0

0 0 0 0

P1-65

1 0 0 0

0 0 0 0

P1-70

0 0 0 0

0 0 0 0

------

TABLE VI. Display driver outputs.

BUS 7

BUS 0

Active

(MSB)

(LSB)

output

0 0 0 0

0 0 0 1

P1-74

0 0 0 0

0 0 1 0

P1-77

0 0 0 0

0 1 0 0

P1-76

0 0 0 0

1 0 0 0

P1-80

0 0 0 1

0 0 0 0

P1-79

0 0 1 0

0 0 0 0

P1-75

0 1 0 0

0 0 0 0

P1-73

1 0 0 0

0 0 0 0

P1-78

10

For Parts Inquires submit RFQ to Parts Hangar, Inc.

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business