MIL-DTL-62739A(AT)

the voltages at all 32 display driver outputs (P1-49 thru P1-80) are not less than

2.75 V.

c. Write each of the bit patterns in table III to the bus and latch them into U3 by

applying the waveforms in figure 3.

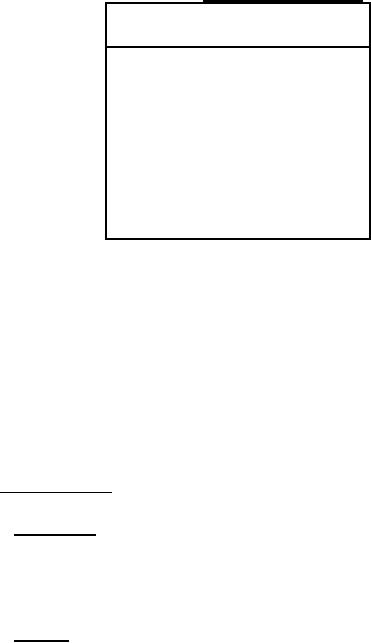

TABLE III. Display driver outputs.

BUS 7

BUS O

Active

(MSB)

(LSB)

output

0 0 0 0 0 0 0 1

P1-50

0 0 0 0 0 0 1 0

P1-53

0 0 0 0 0 1 0 0

P1-52

0 0 0 0 1 0 0 0

P1-56

0 0 0 1 0 0 0 0

P1-55

0 0 1 0 0 0 0 0

P1-51

0 1 0 0 0 0 0 0

P1-49

1 0 0 0 0 0 0 0

P1-54

0 0 0 0 0 0 0 0

------

d. Verify that the voltage at the active output listed in table III for each bit pattern is

not greater than 1.00 V. Verify that each of the 31 display outputs not listed in the

table for each bit pattern have a voltage of not less than 2.75 V.

e. Write each of the bit patterns in table IV to the bus and latch them into U4 by

applying the waveforms in figure 4. Repeat part d.

f. Write each of the bit patterns in table V to the bus and latch them into U5 by

applying the waveforms in figure 5. Repeat part d.

g. Write each of the bit patterns in table VI to the bus and latch them into U6 by

applying the waveforms in figure 6. Repeat part d.

4.2.3.5 Real time clock.

4.2.3.5.1 Clock clear. To determine conformance to 3.3.5.1, 5.00 V shall be applied to

both P1-38 and P1-33. U22 pin 10 shall be verified to maintain a logic level 1. U2 pins 3, 4, 5, 6,

11, 12, 13 and 14, and U21 pins 3, 4, 5, 6, 11, 12, 13, and 14 shall be verified to maintain a logic

level 0.

4.2.3.5.2 Q pulse. To determine conformance to 3.3.5.2, a CMOS voltage level square

wave (frequency between 50 kilohertz (kHz) and 410 kHz) shall be applied to P1-45, and 0.00 V

to P1-43. The voltage level at P1-43 shall be brought to 5.00 V. The rising edge of the Q pulse

at U16 pin 13 and P1-42 shall be verified to meet the timing restrictions of figure 1.

9

For Parts Inquires submit RFQ to Parts Hangar, Inc.

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business