MIL-DTL-62736A(AT)

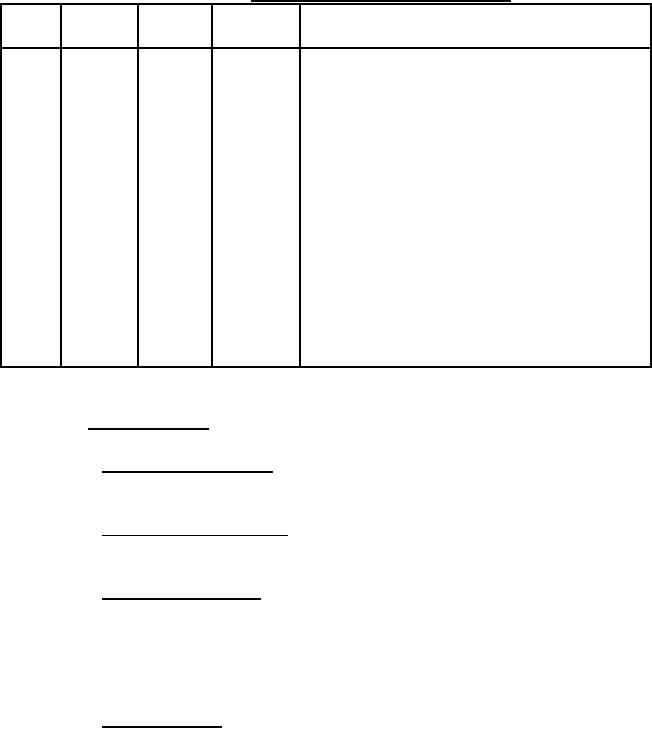

TABLE XXII. Data for MDU divide with overflow.

Latch

Read or High or

Data at P1-

figure Register

Load

Low Byte 28 27 26

25 24

23

22

21

4

Load

Control

High

0

1

1

0

1

1

0

0

4

Load

X

High

0

0

0

0

0

0

0

1

4

Load

Low

0

1

1

1

0

1

1

1

4

Y

Load

High

0

0

0

0

0

1

0

0

4

Load

Low

0

1

0

1

1

0

0

1

4

Z

Load

High

0

0

0

0

0

0

0

0

4

Load

Low

0

1

1

1

1

0

1

1

4

Control

Load

High

0

1

1

0

0

0

1

0

5

X

Read

High

0

0

0

0

0

0

0

1

5

Read

Low

0

1

1

1

0

1

1

1

5

Y

Read

High

X

X

X

X

X

X

X

X

5

Read

Low

X

X

X

X

X

X

X

X

5

Z

Read

High

X

X

X

X

X

X

X

X

5

Read

Low

X

X

X

X

X

X

X

X

Status

5

Read

High

0

0

0

0

0

0

0

1

X = Don't care

4.2.3.8 Communications.

4.2.3.8.1 UART crystal oscillator. To determine conformance to 3.3.8.1, observe the

output of Y1 pin 8 with an oscilloscope.

4.2.3.8.2 Crystal frequency division. To determine conformance to 3.3.8.2, observe the

signals at U5 pins, 6, 5, 3, 2, 4, 13, 12 and 14 with an oscilloscope.

4.2.3.8.3 Frequency select latch. To determine conformance to 3.3.8.3, verify that

U4 pin 1 is at logic level 0. Apply the logic levels in table X at P1-21 through P1-28 and latch

them in by applying the waveforms in figure 2. Apply the logic levels in table XI to P1-21

through P1-28 and latch them into U7 by applying the timing diagram of figure 5. Verify that the

corresponding logic levels in table XI are present at U7 pins 2, 7, and 10.

4.2.3.8.4 Frequency select. To determine conformance to 3.3.8.4, verify that U4 pin 1 is

at logic level 0. Apply the logic levels in table XII to P1-21 through P1-23 and latch them into

U7 by applying the timing diagram in figure 5. Verify that the corresponding frequencies in table

XII are present in U6 pin 5.

20

For Parts Inquires submit RFQ to Parts Hangar, Inc.

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business