MIL-DTL-62736A(AT)

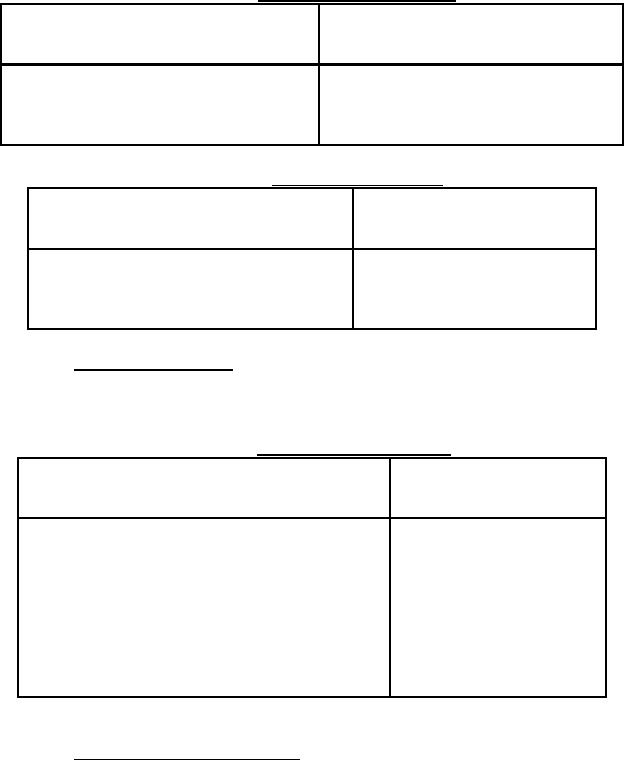

TABLE III. Transceiver bus logic levels.

Applied data

Observed data

P1-

U4 pin

28

27

26 25 24

23

22

21

9

8

7

6

5

4

3

2

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

TABLE IV. Extended I/O latch data.

Applied data

Observed data

P1-

U9 pin

28

27

26

25 24

23

22

21

15

12

10 07

05

02

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

3.3.6.3 Extended I/O decoder. While U4 pin 1 is at logic level 0, the waveforms shown

in figure 2 shall be applied to latch the data shown in table V into U9 and the results shall be

observed at U10.

TABLE V. Extended I/O decoder data.

Applied data

Observed data

P1-

U10 pin

28

27

26

25

24

23

22

21

10

11 12 13

14

X

X

X

X

0

0

0

0

0

0

0

0

0

X

X

X

X

0

0

0

1

0

0

0

0

1

X

X

X

X

0

0

1

0

0

0

0

1

0

X

X

X

X

0

0

1

1

0

0

1

0

0

X

X

X

X

0

1

0

0

0

1

0

0

0

X

X

X

X

0

1

0

1

1

0

0

0

0

X

X

X

X

0

1

1

0

0

0

0

0

0

X

X

X

X

0

1

1

1

0

0

0

0

0

X

X

X

X

1

X

X

X

0

0

0

0

0

(X denotes a don't care condition)

3.3.6.4 BUS transceiver direction logic. U4 pin 1 shall conform to the logic shown in

table VI.

6

For Parts Inquires submit RFQ to Parts Hangar, Inc.

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business