MIL-DTL-62736A(AT)

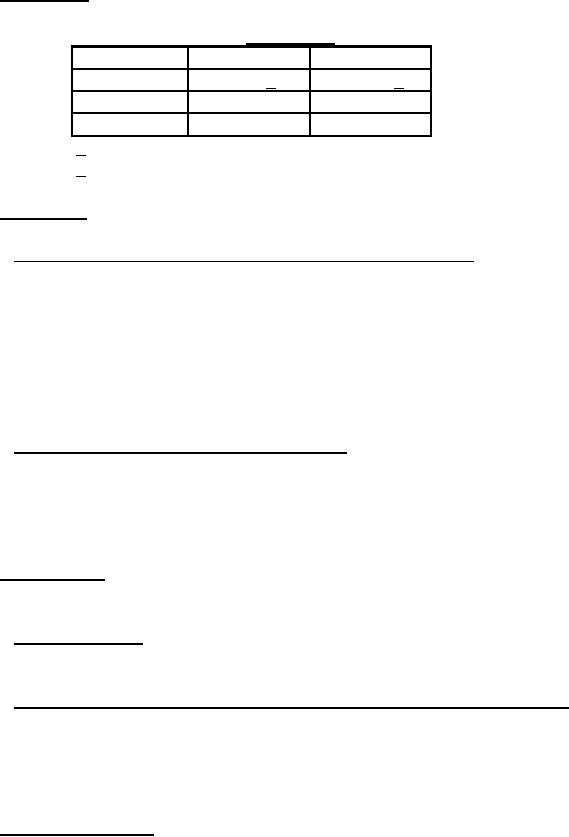

3.3.1 Input power. The PWA shall require not more than the current specified in table I.

TABLE I. Input power.

Source

Voltage

Current

P1-5, 6

5 Vdc 1/

150 mA 2/

P1-13, 14

15 Vdc

7.5 mA

P1-19, 20

-15 Vdc

8.5 mA

1/ Vdc = Volts direct current

2/ mA = milliampere

3.3.2 Logic levels.

3.3.2.1 Complimentary metal oxide semiconductor (CMOS) logic levels. Unless

otherwise specified (see 6.2), CMOS logic levels accepted by and output from the PWA shall be

as follows:

Input High (Logic Level 1) = 3.5 Vdc minimum (min)

Input Low (Logic Level 0) = 1.5 Vdc maximum (max.)

Output High (Logic Level 1) = 4.5 Vdc min

Output Low (Logic Level 0) = 0.5 Vdc max.

3.3.2.2 Transistor-Transistor Logic (TTL) logic levels. Unless otherwise specified

(see 6.2), TTL logic levels accepted by U16 and U17 shall be:

Input High (Logic Level 1) = 2.0 Vdc min

Input Low (Logic Level 0) = 0.8 Vdc max.

3.3.3 Input isolation. (NOTE: A suffix "/" following a capitalized signal name denotes

logic negation.)

3.3.3.1 Data bus isolation. Logic levels applied to any one BUS pin (P1-21 through

P1-28) shall not be affected by logic levels present at any other BUS pin.

3.3.3.2 J3-T, J3-U, IOF/7, MRD/, OEN-Q, OEN-Q/, Q, CLEAR/, and TPB isolation.

Logic levels applied to any one of P1-11/P1-12, P1-15/P1-16, P1-35 through P1-38, P1-57, and

P1-66 shall have no effect on, nor be affected by logic levels applied at any of the other pins

specified in this paragraph. P1-62 should be grounded through a 1 kilohm (Kohm) resistor to

yield appropriate results.

3.3.4 DCA/-15 Vdc source. The voltage at P1-19 and P1-20 shall not be greater than

0.6 Vdc when P1-42 is pulled up to a voltage greater than 0.4 Vdc and less than 32 Vdc.

4

For Parts Inquires submit RFQ to Parts Hangar, Inc.

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business