MIL-DTL-62736A(AT)

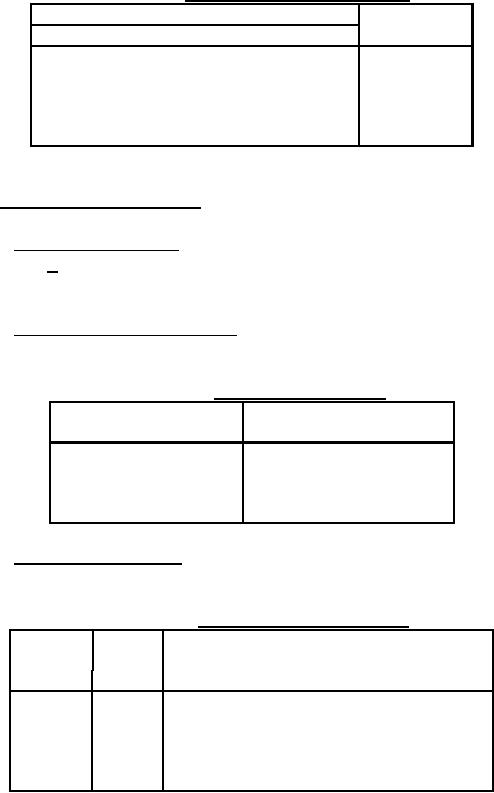

TABLE VI. BUS transceiver direction logic.

Applied data

Observed data

P1-35

P1-36

U10 pin 14

U10 pin 13

U4 pin 1

0

X

X

X

0

X

0

X

X

0

1

1

0

0

0

1

1

0

1

1

1

1

1

0

1

(X denotes a don't care condition)

3.3.7 Multiply/divide unit (MDU).

3.3.7.1 MDU crystal oscillator. The signal at Y2 pin 8 shall have a frequency of

1 megahertz (MHz) + 1 kilohertz (kHz). The rise and fall times of the signal at Y2 pin 8 shall be

less than 150 ns.

3.3.7.2 MDU chip select 1 (CS1) logic. U1 pin 23 shall conform to the logic shown in

table VII.

TABLE VII. MDU select logic levels.

Applied data

Observed data: U1 pin 23,

P1-35 P1-36 P1-57

U2 pin 11, and U3 pin 11

0

X

X

0

1

0

0

1

1

0

1

0

1

1

X

1

3.3.7.3 MDU register selection. The MDU registers shall be selected for either loading or

reading by using the timing diagram of figure 2 and the appropriate data from table VIII.

TABLE VIII. Data to select MDU registers.

Selected

Load

Applied data

MDU

or

P1-

Register

Read

28

27

26 25 24

23

22

21

0

0

1

Status

Read

X

X

1

1

0

0

0

1

Control

Load

X

X

1

1

0

0

0

1

X

Both

X

X

0

0

0

0

0

1

Y

Both

X

X

1

0

0

0

0

1

Z

Both

X

X

0

1

0

(X denotes a don't care condition)

7

For Parts Inquires submit RFQ to Parts Hangar, Inc.

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business