MIL-DTL-62736A(AT)

3.3.5 Reset.

3.3.5.1 Power-up reset. P1-68, U1 pin 21, U2 pin 2, U3 pin 2, U9 pin 1, U12 pin 13, and

U20 pins 1 and 6 shall conform to the timing diagram shown in figure 1 when the voltage at P1-5

and P1-6 is brought from 0 Vdc to +5 Vdc.

3.3.5.2 CLEAR/. Applying a logic level 0 to P1-62 shall bring P1-68 to logic level 0 in

less than 62 nanoseconds (ns).

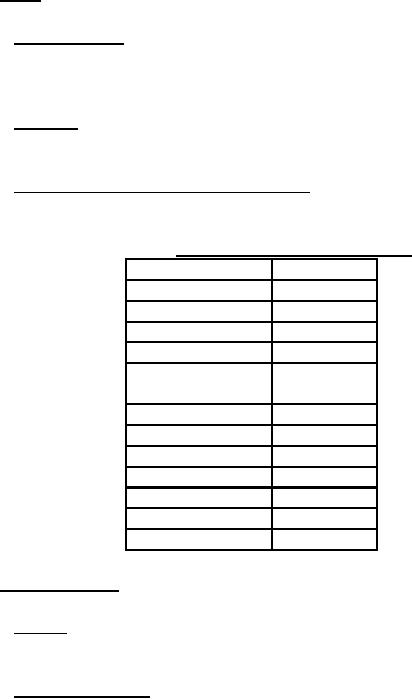

3.3.5.3 States during power-up reset or CLEAR/. While P1-62 is held at logic level 0,

the following pins shall be at the logic level designated in table II.

TABLE II. Logic levels during reset or clear.

Pin

Logic Level

P1-73

1

P1-76

1

P1-79

0

U8 pins 3, 5

0

U9 pins 2, 5, 7,

0

10, 12, 15

U10 pin 10-14

0

U10 pin 15

1

U11 pin 4

1

U12 pins 3, 9, 11

0

P1-75

1

P1-78

1

U1 pins 24, 25

1

3.3.6 BUS transceiver.

3.3.6.1 Data in. With U4 pin 1 at logic level 0, data shall be applied and the results shall

be observed as shown in table III.

3.3.6.2 Extended I/O latch. While U4 pin 1 is at logic level 0, the waveforms shown in

figure 2 shall be applied to latch the data shown in table IV in U9.

5

For Parts Inquires submit RFQ to Parts Hangar, Inc.

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business