MIL-DTL-62737A(AT)

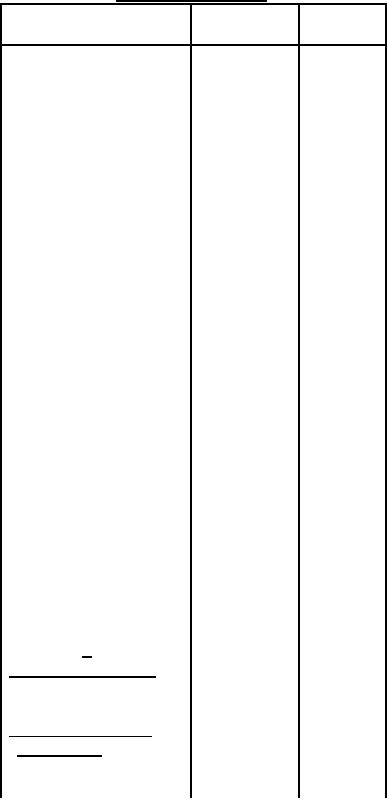

TABLE X. Verification methods - Continued.

Verifica-

Title

Requirement

tion

2 MHz clock

3.3.5.2

4.2.3.5

400 kHz clock

3.3.5.3

4.2.3.5

200 kHz clock

3.3.5.4

4.2.3.5

High order byte address

3.3.6.1

4.2.3.6.1

latch

Microprocessor inputs

3.3.6.2

4.2.3.6.2

I/O port decoder

3.3.7.1

4.2.3.7.1

OEN-Q

3.3.7.2

4.2.3.7.2

OEN-Q/

3.3.7.3

4.2.3.7.3

Data BUS transceiver

3.3.7.4

4.2.3.7.4

logic

Data BUS inputs

3.3.7.5

4.2.3.7.5

External input logic

3.3.7.6

4.2.3.7.6

External inputs

3.3.7.7

4.2.3.7.7

Extended I/O latches and

3.3.7.8

4.2.3.7.8

decoder

Extended I/O data

3.3.7.9

4.2.3.7.9

clocking

3.3.7.10

4.2.3.7.10

Microprocessor clock

frequency select

4.2.3.7.11

Memory bank select

3.3.7.11

Bootstrap EPROM page

3.3.7.12

4.2.3.7.12

select

3.3.7.13

4.2.3.7.13

Memory chip select

4.2.3.8.1

Bootstrap EPROM read

3.3.8.1

3.3.8.2

4.2.3.8.2

SRAM write

4.2.3.8.3

SRAM read

3.3.8.3

3.3.8.4

4.2.3.8.4

EEPROM byte write

3.3.8.5

4.2.3.8.5

EEPROM read

3.3.8.6

4.2.3.8.6

EEPROM page write

4.2.3.9

ATE Test 1/

3.3.9

Interface requirements

3.4

4.2.4

Overall enveloped &

3.4.1

4.2.4.1

interfaces

3.5

4.2.5

Ownership & support

requirements

4.2.5.1

Interchangeability

3.5.1

4.2.5.2

3.5.2

Identification marking

13

For Parts Inquires submit RFQ to Parts Hangar, Inc.

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business