MIL-DTL-62737A(AT)

Input High (Logic Level 1) = 3.5 Vdc minimum (min.)

Input Low (Logic Level 0) = 1.5 Vdc maximum (max.)

Output High (Logic Level 1) = 4.5 Vdc min.

Output Low (Logic Level 0) = 0.5 Vdc max.

3.3.3 Input isolation. (NOTE: A "/" following a capitalized signal name denotes logic

negation.)

3.3.3.1 EF1/ - EF4/, INTERRUPT/, and CLEAR/ isolation. Logic levels applied to any

one of the P1-50, P1-52, P1-53, P1-54, P1-56, and P1-62, shall have no effect on nor be affected

by logic levels applied at any of the other pins specified in this paragraph.

3.3.3.2 External input isolation. Logic levels applied to any one of P1-76, P1-77, P1-79,

P1-81, P1-69, P1-71, P1-73, and P1-75 shall have no effect on nor be affected by logic levels

applied at any of the other pins specified in this paragraph.

3.3.4 Reset.

3.3.4.1 Power-up reset. Signals at pins P1-68, U1-3, U13-1, U13-13, U22-1, U24-4,

U24-10, and U25-4 shall conform to the waveforms shown in figure 1 as +5.0 Vdc is applied to

P1-5 and P1-6.

3.3.4.2 CLEAR/. Applying a logic level 0 to P1-62 shall bring P1-68 to logic level 0 in

less than 62 nanoseconds (ns).

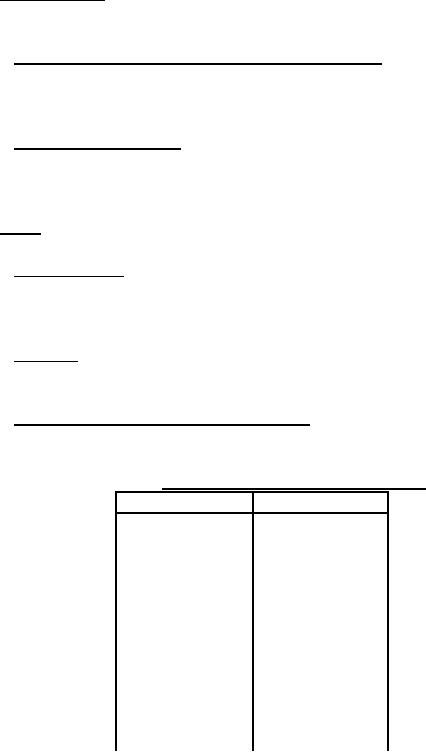

3.3.4.3 States during power-up reset or CLEAR/. While P1-62 is held at logic level 0,

the following pins shall be at the logic level designated in table II.

TABLE II. Logic levels during reset or CLEAR/.

Pin

Logic Level

P1-29

0

P1-30

0

P1-31

0

P1-32

0

P1-33

0

P1-34

0

P1-35

0

P1-37

0

P1-38

0

P1-72

1

U1-4, 17-20

0

U9-20

1

4

For Parts Inquires submit RFQ to Parts Hangar, Inc.

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business