MIL-DTL-62737A(AT)

3.3.7.3 OEN-Q/. The OEN-Q/ signal shall conform to the waveform in figure 3 when the

Q output (U1-4) is at logic level 0.

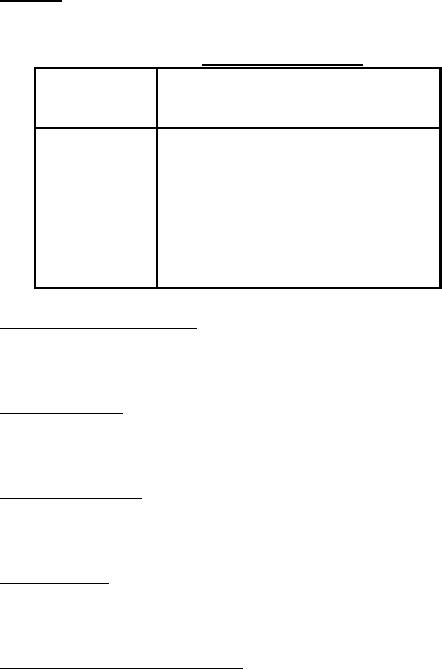

TABLE III. I/O port decoder logic.

I/O decoder output

U11 Pin

P1-

14

3

2

29

30

31 32 33

34

35

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

1

1

0

0

0

1

0

0

0

1

0

0

0

0

0

0

1

0

0

1

0

1

0

0

0

0

0

1

0

1

1

0

0

0

0

0

0

0

1

1

1

1

3.3.7.4 Data BUS transceiver logic. The data BUS transceiver direction pin (U30-8) shall

be at logic level 0 when MRD/ (U19-14) and any of the U1 pins 17, 18, or 19 are at logic level 1.

Otherwise, U30-8 shall be at logic level 1.

3.3.7.5 Data BUS inputs. The logic levels present at P1-21 through P1-28 shall appear at

U21 pins 9, 8, 7, 6, 5, 4, 3, and 2, respectively, when U30-8 is at logic level 0. Otherwise, logic

levels present at U21 pins 9, 8, 7, 6, 5, 4, 3, and 2 shall appear at P1-21 through P1-28.

3.3.7.6 External input logic. The external input output enable pin (U30-11) shall be at

logic level 0 when IOB/3 (U11-7) and MRD/ (U19-14) are at logic level 1. Otherwise, U30-11

shall be at logic level 1.

3.3.7.7 External inputs. Logic levels applied at P1-76, P1-77, P1-79, P1-81, P1-69,

P1-71, P1-73, and P1-75 shall appear at U17 pins 12, 9, 5, 6, 16, 15, 19, and 2 when U30-11 is at

logic level 0. U17 pins 12, 9, 5, 6, 16, 15, 19, and 2 shall not drive the data BUS otherwise.

3.3.7.8 Extended I/O latches and decoder. Logic levels present at U1 pins 15 through 11

shall be latched into U22 and shall be present at U22 pins 2, 5, 7, 10, and 12 respectively, at the

rising edge of OEN-Q (U28-12) when IOF/7 (U11-9) is at logic level 1. The logic levels present

at U23 pins 13, 14, and 15 shall be determined by the logic levels at U22 pins, 2, 5, 7, and 10,

according to table IV.

7

For Parts Inquires submit RFQ to Parts Hangar, Inc.

© Copyright 2015 Integrated Publishing, Inc.

A Service Disabled Veteran Owned Small Business